## Новые проблемы перспективных методик корпусирования

Ключевые слова: интерпозер, корпусирование, кристалл ИС, моделирование, проектирование, этажерка.

Перспективные методы корпусирования ИС получают все большее признание по мере того, как стоимость и сложность интегрирования различных элементов на планарные «системы-на-кристалле» растут. При этом одной из труднейших задач является проверка функционирования и выхода годных приборов, корпусированных при помощи подобных методов.

К проблемам развития перспективных методик корпусирования можно отнести следующие:

- межсоединения SoC и разводка не масштабируются теми же темпами, что и транзисторы;

- затраты на проектирование и изготовление кристаллов ИС растут все быстрее с каждым новым уровнем технологий;

- на каждом новом технологическом уровне обостряются проблемы с сопротивлением, электрической емкостью, тепловыделением и различными типами шумов.

Действительно, отраслевые специалисты отмечают, что до сих пор т.н. «закон Мура» работал без сбоев, но в последние годы возникла растущая проблема увеличения времени задержки сигнала на межсоединениях. Сами транзисторы продолжают масштабироваться, что приводит к снижению связанного с ними времени задержки, однако межсоединения не успевают за масштабированием транзисторов и становятся, пожалуй, самым узким местом при проектировании и производстве ИС.

Все вышеописанные проблемы заставляют изготовителей ИС больше внимания уделять перспективным методикам корпусирования, включая

и 3D-корпусирование, ные варианты «систем-в-модуле» (или в корпусе - system-in-package) а также варианты технологии fan-outs. Последние представляют собой корпусирование на уровне пластины с разветвлением. Наиболее распространен подход FO-WLP (fan-out wafer-level packaging). Это один из видов компромисса между корпусированием на уровне кристалла и корпусированием на уровне пластины. В рамках этой методики полупроводниковая пластина режется на кристаллы и отдельные кристаллы ИС встраиваются в новую «искусственную» пластину. В полученной встраиваемой структуре между отдельными кристаллами образуется достаточно места, что позволяет формировать разветвленный слой перераспределения. Уникальность подхода FO-WLP состоит в том, что, используя стандартный WLP-процесс, можно интегрировать более одного кристалла за счет этажирования. Существует еще один набирающий популярность fan-out подход – технология InFO (integrated fan-out), вариант технологии FO-WLP, предложенный ведущим кремниевым заводом TSMC и реализованный на его базовых технологических процессах.

Стоимость современных заводов по обработке пластин заметно растет по мере перехода на меньшие топологии. Специалисты указывают, что из-

держки производства современных ИС могут быть снижены за счет перехода к 3D-ИС, когда в одном и том же корпусе (модуле) размещаются два или больше кристаллов ИС. При 3D-интеграции сокращаются путь и время прохождения сигнала от одного кристалла ИС к другому — в любом случае они будут короче, чем у крупной планарной ИС (при этом имеется в виду, что при формировании 3D- и планарной ИС использовались одинаковые топологические нормы).

По этому вопросу в полупроводниковой промышленности достигнут консенсус. Отмечается, что перспективные технологии корпусирования становятся реальными независимо от того, как интегрируются кристаллы ИС — «бок-о-бок», с использованием технологии сквозных межсоединений (TSV¹) или интерпозеров². Издержкам на корпусирование уделяется все больше внимания, так как разработка приборов без использования перспективных методик в этой области становится запредельно дорогой.

Использование методик перспективного корпусирования также позволяет сократить объем энергии, необходимой для управления сигналами, — благодаря тому, что межсоединения становятся шире, а пути прохождения сигналов — короче. В некоторых случаях использование перспективных методик кор-

пусирования упрощает гетерогенную интеграцию (интеграцию в одном корпусе или модуле разнородных по типу приборов и используемым топологиям кристаллов ИС), так как вопросы, касающиеся теплоотвода, электромагнитных помех и шума мощности, могут быть решены на этапе поуровневого планирования<sup>3</sup>.

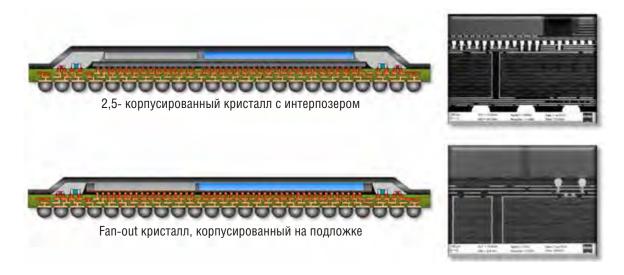

В примерах недостатка нет — процессор A-10 корпорации Apple, сетевые процессоры фирм Cisco и Huawei, различные графические процессоры и архитектуры искусственного интеллекта. Сегодня все ведущие полупроводниковые фирмы ведут разработки конструкций, предусматривающих использование методик перспективного корпусирования (см. рисунок). Правда, многие обнаружили, что подобные подходы не так просты, как кажутся.

В случае, когда удается создать новые конструкции с применением методик перспективного корпусирования, перед производителем ИС открываюся большие перспективы. Но эти методики – не панацея. Проектировщику обычно необходимо решить, какой объем памяти будет сопряжен с центральным процессором, и зачастую этот параметр трудно изменить, так как память уже предварительно размещена на кристалле ИС.

Примеры некоторых методик перспективного проектирования

Скорость передачи данных для некоторых решений может быть очень высокой, но допущенная при проектировании ошибка обойдется недешево: выбрасывать придется не один, а несколько кристаллов ИС, плюс дорогостоящий слой интерпозера. Достижение такого важного показателя,

как требуемый уровень выхода годных в случае с многокристальной конструкцией существенно затрудняется. Разработчики мечтают о модулях типа печатной платы; кроме того, наблюдается значительный интерес к более традиционным «системам-в-корпусе» — без интерпозера.

## НАРАСТАНИЕ СЛОЖНОСТИ

На данный момент интерпозеры представляют собой один из ключевых элементов методик перспективного корпусирования. Все больше кристаллов ИС размещается поверх интерпозеров или на другой подложке в виде контактных столбиков. Для того чтобы понять, насколько это сложно, нужно представить себе несколько трехкристальных этажерок поверх кремниевого интерпозера с восьмью контактными столбиками. В общей сложности – 24 кристалла плюс интерпозер.

Проверить целостность питания конструкции, где каждая трехкристальная этажерка состоит из трех кристаллов ИС типа «система-на-кристалле» (SoC) или из двух кристаллов SoC и одного кристалла памяти, можно только моделированием. При этом собственно моделирование целостности питания конструкции из трехкристальной этажерки поверх интерпозера проблемой не является. Используемые многими разработчиками средства моделирования позволяют выделить необходимые данные из каждого кристалла, включая TSV от кристалла к кремниевому интерпозеру, а также внутренние TSV от нижнего кристалла к интерпозеру, от нижнего к среднему кристаллу и от среднего кристалла к верхнему. При таком сценарии возможно одновременное моделирование целостности электропитания.

Моделирование конструкции с 24 кристаллами требует несколько другого подхода. Один из вариантов - создание модели питания кристалла ИС для одной из этажерок и уплотнение остальных кристаллов в другую модель. При этом важно проверить тепловую целостность среднего кристалла, и лучший способ сделать это – тепловое моделирование. Подобная тепловая модель может быть построена для каждого кристалла, включая кремниевый интерпозер и TSV. И это будет детализированная модель теплового моделирования, которую можно реализовать для каждого из 24 кристаллов, расположенных поверх кремниевого интерпозера.

Новой проблемой, возникающей в 2,5D- и 3D-конструкциях, становится напряженность, индуцированная теплом. В подобных конструкциях обычно используется слой с экстранизким значением диэлектрической проницаемости (ELK, extra low-k), который может пострадать. На возникновение напряженности принято проверять паяные соединения и припой на контактных выступах, но этот новый тип напряженности обусловлен тепловым воздействием и приводит к разрушению материалов. И чем выше температура, тем сильнее напряженность.

## «ЗНАЙ СОСЕДА»

Другая проблема, выявившаяся в перспективных корпусах, – сочетание электромагнитных помех (EMI), электромагнитной совместимости (EMC), электромагнитной восприимчивости (EMS)

и одновременного переключающего выхода (SSO). EMI — это шум, исходящий из прибора, в то время как EMS — шум, поступающий в кристалл извне. В случае SSO сигнал должен проходить в мо-

## **МНЕНИЕ ЭКСПЕРТА**

Кремниевая микроэлектроника за счет уменьшения топологических размеров решает задачи повышения интеграции элементов для увеличения потребительского функционала микросхем и повышения их быстродействия. Однако все усилия по повышению быстродействия кристалла микросхемы на стадии его производства могут быть нивелированы при посадке в корпус кристалла (или нескольких кристаллов при построении SiP) из-за неудачных решений контактов, межсоединительных линий и выводов. Сегодня завершающие операции при создании микроэлектронных изделий стали очень ответственными и дорого-

стоящими: при ошибке в проектировании или неправильно рассчитанной посадке кристалла в корпус высокое время RC-задержки может полностью «обнулить» все заслуги кристального производства. В первом рассмотренном в статье варианте - FlipChip - для каждого нового схемотехнического решения коммутации нескольких кристаллов нужен новый дорогостоящий корпус. Во втором варианте – при применении промежуточной кремниевой платы, имеющей как горизонтальную, так и вертикальную электрическую разводку (интерпозер). – в ряде случаев корпус можно не менять. а заменить только интерпозер. Этот вариант сложнее в реализации, но обладает серьезными преимуществами. НИИМЭ совместно с НИУ МИЭТ ведет работу в области развития технологий интеграции электронных элементов с использованием кремниевых интерпозеров с металлизированными отверстиями диаметром порядка 60 мкм в подложке толщиной 150-360 мкм с переходным сопротивлением не более 70 мОм. В поле нашего внимания находятся также решения коммутации современной ЭКБ с использованием интерпозеров не только при формировании SiP, но и в более сложных системах, например в 3D-сборках с плотной упаковкой однотипных приборных кристаллов или гибридных сборках с высоким уровнем функциональных задач при использовании разнородной ЭКБ.

Александр Итальянцев, начальник объединенного отдела функциональной электроники АО «НИИМЭ»

дуле от одного кристалла к другому. Для этого также требуется предварительно смоделировать ситуацию.

Итак, всеохватывающая проблема проектирования 2,5D- и 3D-гетерогенных структур заключается в том, что по завершении проектирования одного из блоков недостаточно проверить его отдельно от других. Важно учесть, что

произойдет при интеграции одного блока с другим или с целым кристаллом ИС. Вариантов множество — например, по аналогии с человеческими отношениями, знание и понимание того, что делает сосед, может вызвать желание держаться от него подальше. В случае корпусирования такой подход оказался верным для емкостных и резистивных